| CPU, FPU, ALU, etc.: MCU: UVEPROM: SAMPLES: |

ALI

[+] AMD

ATARI GAME

AZUL

BULGARIA

CHIPS

CIRRUS LOGIC

CMD

[+] CYRIX

DEC

EVERGREEN

FAIRCHILD

FREESCALE

FUJITSU

GOLDSTAR

GTE MICRO

HARRIS

HITACHI

HP

[+] IBM

IDT

IIT

INMOS

[+] INTEL

INTERSIL

ISKRA

ITE

KINGSTON

LSI LOGIC

MEDIATEK

MEV

MHS

MITSUBISHI

MME (FWE)

MMN

MOS

MOSTEK

[+] MOTOROLA

NEC

NEOTION

NS

OKI

PHILIPS

RCA

RE

ROCKWELL

SAMSUNG

SESCOSEM

SGS

SHARP

SIEMENS

SIGNETICS

SONY

ST

SUN

SYNERTEK

TESLA

THOMSON

TI

TOSHIBA

TRANSMETA

TRW

TUNGSRAM

ULSI

UMC

UNITRA

[+] USSR-RUS

VIA

VITESSE

VLSI

WDC

WEITEK

ZARLINK

ZFTM (ZMD)

ZILOG

-----------

FAKE

SIGNETICS

| n.n. | Model | Package | Additional description |

|

1 2 3 4 5 6 7 |

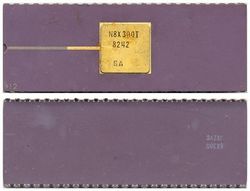

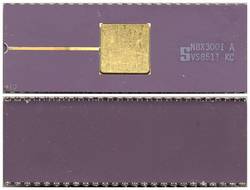

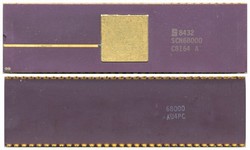

N3002N 2650AN N8X300I N8X300I A N8X305N N8X305N A SCN68000 |

PDIP-28 PDIP-40 CDIP-50 CDIP-50 PDIP-50 PDIP-50 CDIP-64 |

7821; Bit Slice Processor 8233; 8-bit microprocessor 8242 VS8511 KC KEY8432 8825KA; 1820-3422 KK8605 DO 8432; SCN68000; C8I64 A |

|

|

|

||||||||

| 1 | 2 | 3 | N8X300I | |||||||

|

Clock cycle time (min.): Clock cycle time (typ.): I/O bus: Vcc: |

70 ns (14.29 MHz) 45 ns 2 bit 5 V ± 5% |

Frequency: Data bus (ext.): Addresing range: Vcc: TDP: Technology: |

1.25 MHz 8 bit 32 K 5 V ± 5% 525 mW NMOS |

Processor cycle time: I/O bus: Instruction bus: Instruction address bus: Vcc: |

250 ns 8 bit 16 bit 13 bit 5 V ± 5% |

|||||

|

Separate buses for instruction, instruction address and

3-state I/O; Bipolar low-power Schottky technology; TTL inputs and outputs |

||||||||||

|

|

|

||||||||

| 4 | 5 | 6 | N8X305N A | |||||||

|

Processor cycle time: I/O bus: Instruction bus: Instruction address bus: Vcc: |

250 ns 8 bit 16 bit 13 bit 5 V ± 5% |

Processor cycle time: I/O bus: Instruction bus: Instruction address bus: Vcc: |

200 ns 8 bit 16 bit 13 bit 5 V ± 5% |

Processor cycle time: I/O bus: Instruction bus: Instruction address bus: Vcc: |

200 ns 8 bit 16 bit 13 bit 5 V ± 5% |

|||||

|

Separate buses for instruction, instruction address and

3-state I/O; Bipolar low-power Schottky technology; TTL inputs and outputs |

Separate buses for instruction, instruction address and

3-state I/O; Bipolar low-power Schottky technology; TTL inputs and outputs |

Separate buses for instruction, instruction address and

3-state I/O; Bipolar low-power Schottky technology; TTL inputs and outputs |

||||||||

|

|

|||||||||

| 7 |

|

|||||||||

|

Frequency: Data bus (ext.): Address bus: Vcc: |

8 MHz 16 bit 24 bit 5 V ± 5% |

|||||||||