| CPU, FPU, ALU, etc.: MCU: UVEPROM: SAMPLES: |

[-] USSR-RUS

ALU

145

580

581

582

583

584

585

587

588

589

757

1013

1518

1801

1802

1804

1806

1807

1810

1811

1815

1818

1821

1824

1831

1838

1839

1843

1858

1867

1914

MK1

T34

Т36

Z80

USSR 1831

| n.n. | Model | Package | Additional description | Аналог |

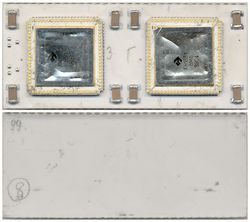

| 1 | КН1831ВМ1+КН1831ВУ1 | CLCC/CDIP-60 | КН1831ВМ1; 8904 + КН1831ВУ1; 8902; Электроника, Воронеж | DCJ-11 |

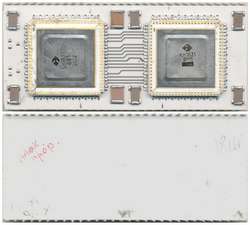

| 2 | КН1831ВМ1+КН1831ВУ1, var.2 | CLCC/CDIP-60 | КН1831ВМ1 + КН1831ВУ1; 9102; Электроника, Воронеж | DCJ-11 |

|

|

|

||||||||

| 1 | 2 | КН1831ВМ1+КН1831ВУ1 var.2 | ||||||||

|

Технология: Шифр темы разработки ВМ1: Шифр темы разработки ВУ1: |

КМОП Теорема 2 Тунгус 1 |

|||||||||

|

КН1831ВМ1 - микропроцессорная СБИС для

выполнения функция обработки данных и управления памятью - совмещенная шина адреса и данных: 16-разрядов; - дополнительная шина адреса: 6 разрядов; - объем адресуемой памяти: 4 МБ; - прямая адресация памяти: 128 КБ; - система команд: 140; - разрядность данных с фиксированной запятой: 8, 16, 32, 64; - разрядность данных с плавающей запятой: 32, 64; - время цикла микрокоманд: 260 нс; - напряжение питания: (5 ± 5%) В; - потребляемая мощность: не более 0,5 Вт КН1831ВУ1 - СБИС микропрограммного управления - совмещенная шина адреса и данных: 16-разрядов; - шина микрокоманд: 22 разряда; - общее кол-во линий запросов прерываний: 9; - объем микропрограммной памяти: 40 кбит; - напряжение питания: (5 ± 5%) В. |

||||||||||

| Литература: А.В.Нефедов "Интегральные микросхемы и их зарубежные аналоги. Серии К1815-К6500" Том 12, Москва 2001 | ||||||||||